Samsung & SK hynix Eye 1c DRAM As The Choice For HBM4 Memory, TSMC Preps HBM4 Base Dies On 12nm & 5nm

Samsung & SK hynix Eye 1c DRAM As The Choice For HBM4 Memory, TSMC Preps HBM4 Base Dies On 12nm & 5nm

Development on the next-gen HBM4 memory standard is in full swing as TSMC, Samsung & SK hynix prep the latest DRAM & process nodes.

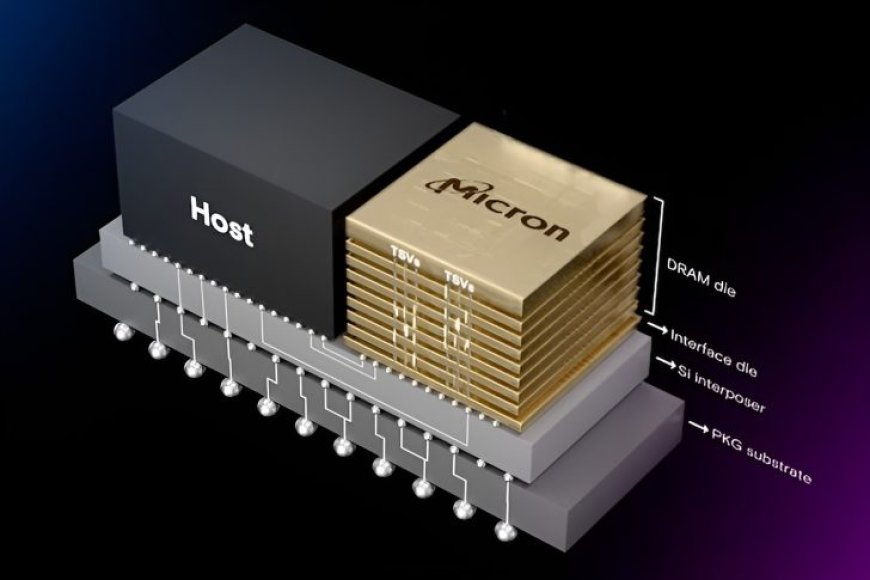

Both Samsung and SK hynix are in the race to offer the next-generation HBM4 memory standard. The Korean giants have shown their initial plans for a 2025-2026 debut. Samsung has so far eyed the use of 3D Packaging technologies and up to 16-Hi stacks for an unprecedented increase in the VRAM capacities and memory bandwidth while SK hynix also plans to incorporate new packaging technologies for its own HBM4 solutions.

According to the latest industry sources quoted by ZDNet Korea, it is stated that Samsung and SK hynix are planning to use 1c DRAM to power the next-generation HBM4 memory. It is reported that Samsung initially planned the use of its 1b DRAM (10-nano class 5th Gen DRAM) for HBM4 which began production last year in May while its existing HBM3E products are based on the 1a DRAM. The company plans to regain its lost momentum since it was recently reported that Samsung had failed to pass qualification tests for NVIDIA's latest AI GPUs such as Hopper and Blackwell.

A key reason highlighted for the use of the 1c DRAM is that Samsung sees it behind its rivals when it comes to power consumption. As such, the 1c DRAM will be used across 12-Hi and 16-Hi HBM4 products. The company is expected to build its first mass production line for the 1c DRAM by the end of 2024 and the total production capacity for this is going to be around 3000 units per month. The final HBM4 product figures shouldn't be that much different either. Certain sources even high-light that Samsung might initiate mass production earlier by mid-2025 but that isn't confirmed yet.

SK hynix plans to utilize the 1b DRAM for the HBM4 memory products while 1c DRAM will be used by the manufacturer for the next-gen HBM4E memory.

But that's not all, during the TSMC European Technology Symposium 2024, the semiconductor maker reported that due to the complexities with the HBM4 memory moving from 1024-bit to 2048-bit interfaces, new base dies will be made using the N12 and N5 process nodes.

"We are working with key HBM memory partners (Micron, Samsung, SK Hynix) over advanced nodes for HBM4 full stack integration," said Senior Director of Design and Technology Platform at TSMC. "N12FFC+ cost effective base die can reach HBM for performance and N5 base die can provide even more logic with much lower power at HBM4 speeds."

"We collaborate with EDA partners like Cadence, Synopsys, and Ansys to certify HBM4 channel signal integrity, IR/EM, and thermal accuracy," the TSMC representative explained.

TSMC via Anandtech

The new base dies will be used to make memory products with up to 16-Hi stacks by leveraging CoWoS technologies such as the CoWoS-L and CoWoS-R packages that were revealed recently. It will also leverage a new channel signal integrity process among other key changes. Having a 5nm node will provide benefits in power, performance and density so we look forward to the release of next-generation HBM4 memory products in the coming year for next-gen GPU accelerators.

What's Your Reaction?