Intel Falcon Shores XPU To Push High-Performance Computing To The Extreme With Multi-Tiled x86 CPU & Xe GPU Configurations, Targeting Over 5x Performance Per Watt

Intel Falcon Shores XPU To Push High-Performance Computing To The Extreme With Multi-Tiled x86 CPU & Xe GPU Configurations, Targeting Over 5x Performance Per Watt

Earlier this year, Intel revealed its Falcon Shores XPU lineup which is a new scalable chip design, utilizing x86 and Xe cores for supercomputing workloads. Today, at ISC 2022, Intel is disclosing further information and configurations that we can expect from Falcon Shores.

The Intel Falcon Shores XPU is a brand new chip segment that will be based around the company's Xeon platform. The XPU architecture isn't a simple CPU & GPU combination but has several brand new technologies integrated that will make them stand out from the rest of the chip segment. The XPUs may seem a lot like the Exascale APUs that AMD has been working on for some time and are expected to debut sometime next year with the Instinct MI300 solution which will combine Zen and CDNA chiplets together.

Looking ahead, Falcon Shores is the next major architecture innovation on our roadmap, bringing x86 CPU and Xe GPU architectures together into a single socket. This architecture is targeted for 2024 and is projected to deliver benefits of more than 5x performance-per-watt, 5x compute density, 5x memory capacity, and bandwidth improvements.

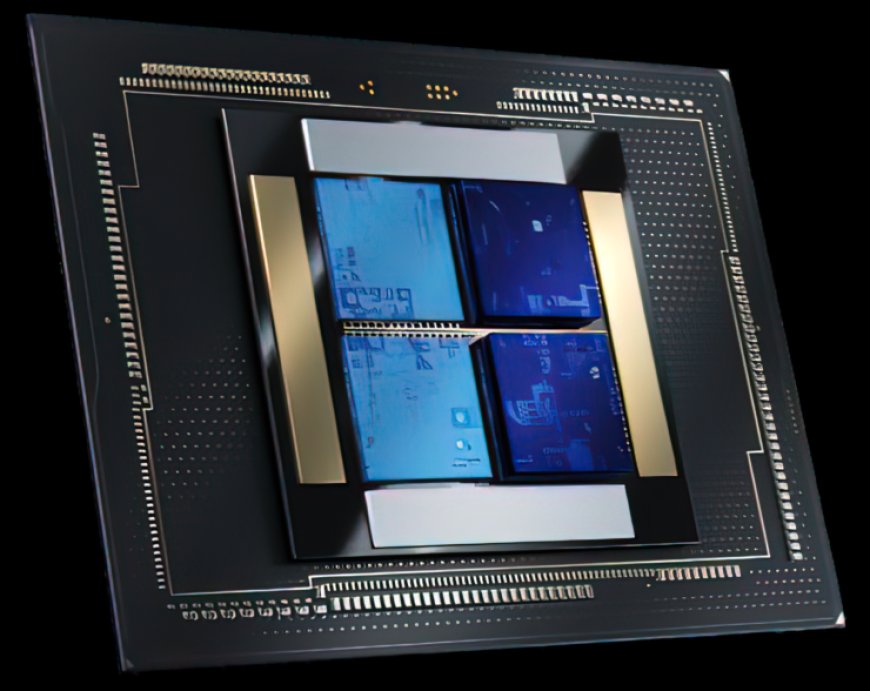

Intel terms Falcon Shores XPU as a 'New Tile-Based Flexible & Scalable Architecture'. We can see that tiles will be a fundamental part of Intel's next-generation chips whether they be CPUs, GPUs, or XPUs. Intel has shown three configurations (For Illustrative Purposes Only), a full-on x86 Tiled solution, a Xe GPU Tiled solution, and one which makes use of both x86 CPU and Xe GPU cores.

All three configurations are interesting in their own sense but what's common amongst all four designs is that they feature at least four Tiles. That's the same Tile layout as the Intel Sapphire Rapids Xeon CPU lineup. There's no solution with HBM currently mentioned but that may also come later. As for what Falcon Shores XPUs bring to the table, some of the highlighted features include:

Considering that Intel has mentioned an 'Angstrom' Era process node for Falcon Shores XPUs, we can either expect them to be based on the 20A or 18A node. Based on the roadmap, the XPUs are expected to launch around 2024-2025. Furthermore, they will be sharing extreme bandwidth via a memory interface that would supposedly be based on the HBM standard or an integrated cache solution. Intel also states the use of next-gen advanced packaging technologies to design the new XPUs which means that these chips are definitely going to be much more complex to design than a standard monolithic chip. We are talking about next-gen EMIB & Foveros technologies in action too.

Finally, Intel has shared some preliminary performance benefits of its Falcon Shores XPU design which will offer:

*Performance targets based on estimates relative to current platforms in February 2022.

The whole Intel Falcon Shores XPU platform will be tuned around the oneAPI software suite, offering an open-source solution for local and remote monitoring and managing of Data Center class chips. The Falcon Shores family is still early in development so expect Intel to reveal more details during upcoming events.

What's Your Reaction?