Intel 4 “PowerVia” Chip Demo With E-Core Implementation To Show Benefits of Backside Power Delivery

Intel 4 “PowerVia” Chip Demo With E-Core Implementation To Show Benefits of Backside Power Delivery

Intel will soon be showcasing its next-generation & backside power delivery technology known as PowerVia in an "Intel 4" E-Core chip.

The first look at this implementation of Intel's PowerVia has been tweeted by the VLSI and will be demoed during the 2023 Symposium on VLSI which commences in June. In the tweet, VLSI shows Intel's implementation of PowerVia on the backside of a chip that is mentioned to utilize the "Intel 4" process node and carries an all-E-Core implementation.

#VLSI2023 Highlight paper T1-1 “E-Core Implementation in Intel 4 with PowerVia (Backside Power) Technology” – Intel Corp.Intel reports a high-yielding backside power delivery technology, PowerVia Technology*, and Intel E-Core Implementation in PowerVia Technology. pic.twitter.com/0us9rbUvQr

— IEEE Symposium on VLSI Technology and Circuits (@VLSI_2024) May 2, 2023

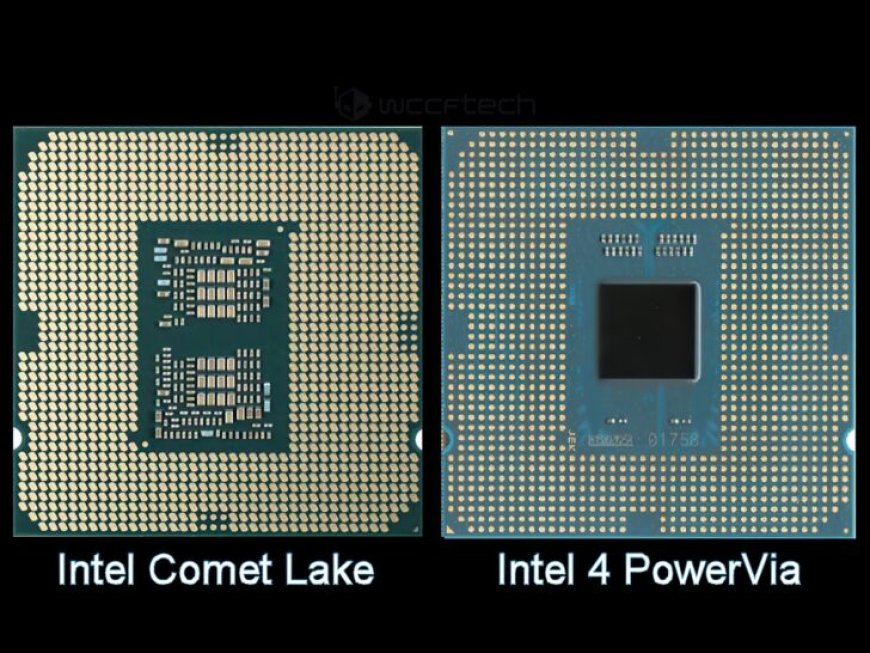

The Intel 4 chip looks like it's based around the older LGA1151/LGA1200 design due to its squared shape and has a secondary die underneath the package. This is the area where you'd usually see large amounts of small transistors but the majority of those have been replaced by the PowerVia technology. Considering that the E-Core implementation is based on "Intel 4", it is likely based on the upcoming Crestmont architecture which powers Meteor Lake's E-Cores.

Furthermore, a cell utilization charge shows that in an area of 2.9mm2 within the chip, the Intel PowerVia tech can hit up to 90% utilization. Furthermore, it's not just the utilization that becomes better but also leads to slight clock speed improvements with reduced IR drop achieving 5% higher clocks on the same chip.

More interestingly, VLSI says that this is a high-yielding design but won't be appearing until at least Arrow Lake or Lunar Lake generations. The reason is that PowerVia and RibbonFET are going to be adopted in consumer-level chips by the 20A and 18A process nodes. The first PowerVia chips are already said to go into volume production by 2024.

From earlier, we know that the PowerVia is a power delivery process that works in the backside to solve bottleneck issues within the interconnect seen in silicon architectures. It is a common problem that PowerVia should solve once it is available. Instead of interconnects transmitting data communication signals and power to the top of the transistor layer, Power Via will deliver directly to the backside of the silicon wafer while simultaneously transmitting signals on top of the wafer.

We can't wait to see what PowerVia does and see it in action in the coming months as it definitely sounds like a technology that can change the landscape in terms of power delivery.

News Source: Tomshardware

What's Your Reaction?