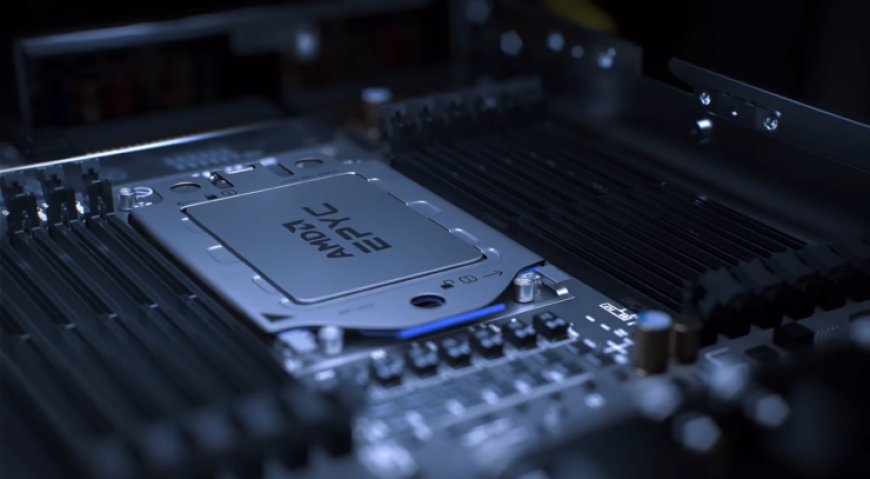

AMD EPYC Milan-X Server CPUs Leak Out, Up To 64 Zen 3 Cores & Possibly 3D V-Cache Stacks

AMD EPYC Milan-X Server CPUs Leak Out, Up To 64 Zen 3 Cores & Possibly 3D V-Cache Stacks

AMD's next-generation EPYC Milan-X CPUs which will feature 3D Chiplet packaging has leaked out by Momomo_US. The lineup will serve as an intermediary solution before the Zen 4 powered EPYC Genoa lineup arrives later in 2022-2023.

AMD has so far confirmed that it is bringing 3D V-Cache chip stacking technology to its Zen 3 core architecture. The technology would first be introduced on next-generation Ryzen Desktop CPUs & from the looks of it, another major product in the works with 3D V-Cache is Milan-X. AMD Milan-X has been known for a while and will be similar to existing Milan EPYC 7003 CPUs except they'll get major changes in the form of chiplet stacking.

EPYC 73○○X(੭ु´・ω・`)੭ु⁾⁾

— 188号 (@momomo_us) August 25, 2021

Following are the AMD EPYC 7003X Milan-X SKUs that were leaked:

Interestingly, all four SKUs listed here retain the same core counts as current variants so we aren't going to see CCD upon CCD level stacking so soon. The CCDs retain their integral cache count but will get a boost from the added SRAM cache through chiplet stacking.

Now what we know about the 3D V-Cache technology is that it is achieved through the use of Micro Bump (3D) & several TSV interconnects. The interconnect uses a brand new hydrophilic Dielectric-Dielectric Bonding with Direct CU-CU bonding which was designed and co-optimized in partnership with TSMC. The two individual silicons (chiplets) are bonded together using this technology. The 3D technology features 9 Micron Pitch bonds.

A single 3D V-Cache stack would incorporate 64 MB of L3 cache that sits on top of the TSV's already featured on existing Zen 3 CCD's. The cache will add upon the existing 32 MB of L3 cache for a total of 96 MB per CCD. AMD also stated that the V-Cache stack can go up to 8-hi which means a single CCD can technically offer up to 512 MB of L3 cache in addition to the 32 MB cache per Zen 3 CCD. So with a 64 MB of L3 cache, you can technically get up to 768 MB of L3 cache (8 3D V-Cache CCD stacks = 512 MB) which will be a mammoth increase in cache size.

3D V-Cache could just be one aspect of the EPYC Milan-X lineup. AMD might introduce faster clocks as 7nm continues to mature and we can see much faster performance from these stacked chips. It is also interesting that the OPN codes for these processors are ready which means that a launch by late 2022 is highly likely which would mean Milan-X might be the first chip to introduce 3D V-Cache.

What's Your Reaction?