AMD EPYC 9755 CPU Spotted: 128 “Zen 5” CPU Cores, 256 Threads, Up To 4.1 GHz Clocks & 650 MB of Cache

AMD EPYC 9755 CPU Spotted: 128 “Zen 5” CPU Cores, 256 Threads, Up To 4.1 GHz Clocks & 650 MB of Cache

AMD's next-gen EPYC Turin CPU, the 9755, featuring an incredible 128 cores and 256 threads with a massive pool of cache has been spotted.

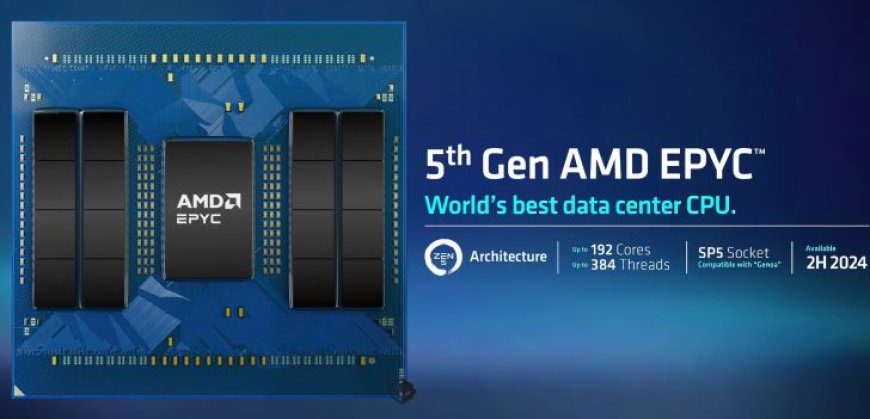

AMD's upcoming 5th Gen EPYC CPUs, codenamed Turin, are going to take core counts to the extreme. With up to 128 cores with the classic Zen 5 architecture and up to 192 cores with the density-optimized Zen 5C architecture. Both of these chips will go on to power the next-gen of data centers, offering big uplifts in performance.

While we have previously covered the full lineup along with actual engineering samples, it looks like one ES chip has been spotted by HXL (@9550pro) and well, it's a beast, to say the least. An alleged 64-core EPYC Turin CPU also leaked out a while ago with its performance benchmarks which you can see here. What you're looking at is the AMD EPYC 9755, one of the many SKUs within the Turin family.

This chip features 128 cores and 256 threads. You can see that the task manager is filled with columns upon columns of threads. Other details revealed by the source are 2.70 GHz base clocks and 4.10 GHz boost clock speeds. Now it is not mentioned if these are the final clocks but the current 4th Gen flagship, EPYC 9654, boosts up to 3.7 GHz so 4.10 GHz clock speeds are quite the uplift.

The other interesting aspect of this leaked CPU is that the AMD EPYC 9755 features a huge pool of cache. We are talking 512 MB or 1 GB of L3, 128 MB of L2, and 10 MB of L1 cache. This gives us a combined total of 650 MB of cache. The current EPYC 9654 CPU features just 384 MB of L3 cache and 96 MB of L2 cache.

We know that AMD's EPYC Turin "Zen 5" SKUs are composed of up to 16 CCDs while the "Zen 5C" SKUs are equipped with 8 CCDs. That would mean that each CCD packs 8 cores (16x8) and each CCD also packs 4 MB of L3 cache.

Since this was a dual-socket configuration, there are 256 cores and 512 threads running in total with up to 1 GB of L3 cache, 256 MB of L2 cache, and 20 MB of L1 cache for a combined total of 1276 MB cache. This is a 31% uplift in cache sizes versus the previous Zen 4 flagships and we can only expect them to be massive once the 3D V-Cache "Turin-X" CPUs hit shelves next year.

AMD EPYC 9965

192c384t

500W TDP

— HXL (@9550pro) July 23, 2024

In addition to the EPYC 9755 CPU, HXL also posts details of another SKU, the 5th Gen EPYC 9965 which is based on the Zen 5C architecture and features 192 cores, 384 threads, and a TDP of 500 watts.

AMD is expected to launch its 5th Gen EPYC CPUs later this year which will compete with Intel's Xeon 6000P and Xeon 6000E families featuring 128 P-Cores and 288 E-Cores, respectively. This will be after a long time that Intel will have core-count parity with AMD's EPYC lineup so the rest would fall to which architecture has the best IPC, Efficiency, and overall performance.

What's Your Reaction?